# unit 2: LOGIC GATES

## AND gate

A gate is simply an electronic circuit which operates a one or more signals to produce an output signal. The output is high only for certain combination of input signals.

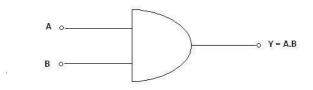

An AND gate (Figure 1.1) has a high output only when all inputs are high. The output is low when any one input is low.

Figure 1.1 AND gate

Boolean expression for AND gate operation is

Y=A . B

## **Truth table**

| А | В | $\mathbf{Y} = \mathbf{A} \cdot \mathbf{B}$ |

|---|---|--------------------------------------------|

| 0 | 0 | 0                                          |

| 0 | 1 | 0                                          |

| 1 | 0 | 0                                          |

| 1 1 | 1 |  |

|-----|---|--|

|-----|---|--|

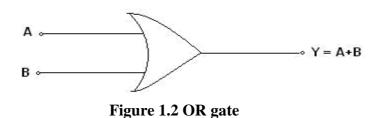

#### **OR** gate

An OR gate (Figure 1.2) produces a high output when any or the entire inputs are high. The output is low only when all the inputs are low.

The Boolean expression for an OR gate is

Y = A + B

## **Truth table:**

| А | В | $\mathbf{Y} = \mathbf{A} + \mathbf{B}$ |

|---|---|----------------------------------------|

| 0 | 0 | 0                                      |

| 0 | 1 | 1                                      |

| 1 | 0 | 1                                      |

| 1 | 1 | 1                                      |

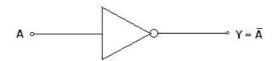

#### NOT gate:

A NOT gate (Figure 1.3) is also called an inverter. The circuit has one input and one output. The output is the complement of the input. If the input signal is high, the output is low and vice versa.

Figure 1.3 NOT gate

The Boolean expression for NOT gate is

$Y = \overline{A}$

**Truth table:**

| Α | $Y = \overline{A}$ |

|---|--------------------|

| 0 | 1                  |

| 1 | 0                  |

If two NOT gates are cascaded then the output will be same as the input and the circuit is called buffer circuit.

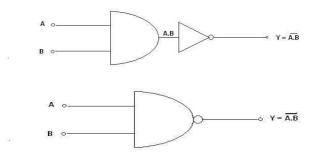

#### NAND gate

A NAND (Figure 1.4) gate has two or more input signals but only one output signal. All input signals must be high to get a low output. When one AND gate is combined with a NOT gate, a NAND gate is obtained.

Figure 1.4 NAND gate

#### **Truth table:**

| А | В |                            |

|---|---|----------------------------|

|   |   | $Y = \overline{A \cdot B}$ |

| 0 | 0 | 1                          |

| 0 | 1 | 1                          |

| 1 | 0 | 1                          |

| 1 | 1 | 0                          |

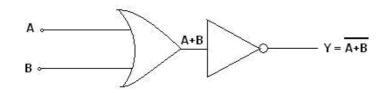

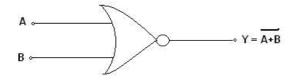

#### NOR gate:

NOR gate (Fig. 1.5) has two or more input signals and one output signal. It consists of one OR gate followed by an inverter. A NOR gate produces a high output only when all the inputs are low.

Figure 1.5 NOR gate

#### Truth table:

| А | В | $Y=\ \overline{A+B}$ |

|---|---|----------------------|

| 0 | 0 | 1                    |

| 0 | 1 | 0                    |

| 1 | 0 | 0                    |

| 1 | 1 | 0                    |

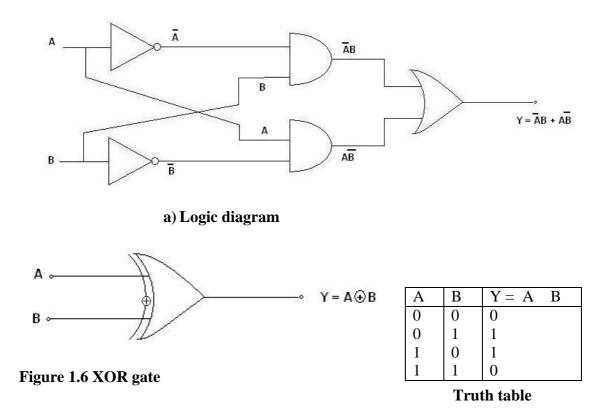

## **XOR** gate

XOR (Figure 1.6) gate is an abbreviation of exclusive OR gate. It has two inputs and one output. For a two input XOR gate, the output is high when the inputs are different and the output is low when the inputs are same. In general, the output of an XOR gate is high when the number of its high inputs is odd. The Boolean expression of the XOR gate is

$$\mathbf{Y} = \mathbf{A}.\mathbf{B} + \mathbf{A}.\mathbf{B}$$